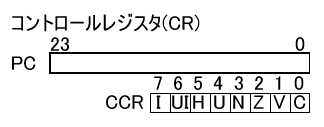

3.1 コンディションコードレジスタ

(1)プログラムカウンタ(PC)

| CPUが次に実行する命令のアドレスを示しています. |

(2)コンディションコードレジスタ(CCR)

| 8ビットのレジスタで,CPUの内部状態を示しています.割り込みマスクビット(I)とハーフキャリ(H),ネガティブ(N),ゼロ(Z),オーバーフロー(V),キャリ(C)の各フラグを含む8ビットで構成されています. |

ビット7:割り込みマスクビット(I) 割り込みマスクビットが1にセットされると,割り込みがマスクされます. ビット6:ユーザビット/割り込みマスクビット(UI) ソフトウェアでリード/ライトできます.割り込みマスクビットとしても使用可能です. ビット5:ハーフキャリフラグ(H) ビット3,11,27にキャリまたはボローが生じたとき1にセットされ,生じなかったとき0にクリアされます. ビット4:ユーザビット(U) ソフトウェアでリード/ライトできます. ビット3:ネガティブフラグ(N) データの最上位ビットを符号ビットとみなし,最上位ビットの値を格納します. ビット2:ゼロフラグ(Z) 演算結果がゼロのとき1にセットされ,ゼロ以外のとき0にクリアされます. ビット1:オーバーフローフラグ(V) 算術演算命令の実行により,オーバーフローが生じたとき1にセットされます.それ以外のとき0にクリアされます. ビット0:キャリフラグ(C) 演算の実行により,キャリが生じたとき1にセットされ,生じなかったとき0にクリアされます.キャリには次の種類があります.

また,キャリフラグには,ビット操作命令で使用されます. |

|

| ◆ 記号の意味

CCR: コンディションコードレジスタ I: 割込みマスクビット UI: ユーザビット/割込みマスクビット H: ハーフキャリフラグ U: ユーザビット N: ネガティブフラグ Z: ゼロフラグ V: オーバーフローフラグ C: キャリフラグ 図3.2 コントロールレジスタ コンディションコードレジスタは,演算命令により処理されたデータの値に応じて自動的に書き換えられます. 今回の実験の条件分岐命令(Bcc)で主に使用するのは,N(ネガティブ)フラグ,Z(ゼロ)フラグの各フラグです. |