4.2.2 チャネル別のコントロールレジスタ

各チャネル毎に用意されているコントロールレジスタには次のようなものがあります.

| 名称 (* はチャネル番号) | 略称 (*はチャネル番号) |

R/W | 初期値 | レジスタアドレス | ||||

|---|---|---|---|---|---|---|---|---|

| CH0 | CH1 | CH2 | CH3 | CH4 | ||||

| タイマコントロールレジスタ* | TCR* | R/W | H'80 | H'FF64 | H'FF6E | H'FF78 | H'FF82 | H'FF92 |

| タイマI/Oコントロールレジスタ* | TIOR* | R/W | H'88 | H'FF65 | H'FF6F | H'FF79 | H'FF83 | H'FF93 |

| タイマインタラプトイネーブルレジスタ* | TIER* | R/W | H'F8 | H'FF66 | H'FF70 | H'FF7A | H'FF84 | H'FF94 |

| タイマステータスレジスタ* | TSR* | R/(W) | H'F8 | H'FF67 | H'FF71 | H'FF7B | H'FF85 | H'FF95 |

| タイマカウンタ*H | TCNT*H | R/W | H'00 | H'FF68 | H'FF72 | H'FF7C | H'FF86 | H'FF96 |

| タイマカウンタ*L | TCNT*L | R/W | H'00 | H'FF69 | H'FF73 | H'FF7D | H'FF87 | H'FF97 |

| ジェネラルレジスタA*H | GRA*H | R/W | H'FF | H'FF6A | H'FF74 | H'FF7E | H'FF88 | H'FF98 |

| ジェネラルレジスタA*L | GRA*L | R/W | H'FF | H'FF6B | H'FF75 | H'FF7F | H'FF89 | H'FF99 |

| ジェネラルレジスタB*H | GRB*H | R/W | H'FF | H'FF6C | H'FF76 | H'FF80 | H'FF8A | H'FF9A |

| ジェネラルレジスタB*L | GRB*L | R/W | H'FF | H'FF6D | H'FF77 | H'FF81 | H'FF8B | H'FF9B |

| バッファレジスタA*H | BRA*H | R/W | H'FF | - | - | - | H'FF8C | H'FF9C |

| バッファレジスタA*L | BRA*L | R/W | H'FF | - | - | - | H'FF8D | H'FF9D |

| バッファレジスタB*H | BRB*H | R/W | H'FF | - | - | - | H'FF8E | H'FF9E |

| バッファレジスタB*L | BRB*L | R/W | H'FF | - | - | - | H'FF8F | H'FF9F |

このうち,本実験では,タイマの動作を設定するTCR(タイマコントロールレジスタ),カウント値を格納するTCNT(タイマカウンタ),動作を行うタイミングのカウント値を設定するジェネラルレジスタ(GRA,GRB)をよく使用します.ここでは,TCR(タイマコントロールレジスタ)について説明します.

TCR(タイマコントロールレジスタ:TCR0〜TCR4) (H'FFFF64,H'FFFF6E,H'FFFF78,H'FFFF82,H'FFFF92) TCRでは,各チャネルのカウンタTCNTのクリア条件の設定や,カウント動作の条件を定めるクロックエッジの設定,カウント動作を行うクロック周波数を決めるためのタイマプリスケーラの設定を行います. なお,CH0〜CH4のそれぞれにTCR0〜TCR4が対応しています |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 略称と機能 | - | CCLR1 | CCLR0 | CKEG1 | CKEG0 | TPSC2 | TPSC1 | TPSC0 |

| リザーブビット | カウントクリア | クロックエッジ | タイマプリスケーラ | |||||

| 初期値 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 本実験での設定 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

|

CCLR0,1(カウンタクリア):カウンタTCNTの値をクリアする条件を設定します. |

| 説明 | CCLR1 | CCLR0 |

| カウンタTCNTのクリアを禁止します. | 0 | 0 |

| TCNTとGRAの値のコンペアマッチ(一致)でTCNTをクリアします. | 0 | 1 |

| TCNTとGRBの値のコンペアマッチでTCNTをクリアします.(本実験ではこの設定を使用します) | 1 | 0 |

| 同期動作中の他のTCNTのカウンタクリアに同期してTCNTをクリアします. | 1 | 1 |

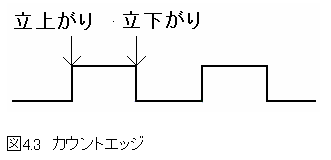

| CKEG0,1(クロックエッジ):TCNTのカウントをクロックの立上がり/立下がり/両エッジのいずれで行うかを設定します. |

| 説明 | CKEG1 | CKEG0 |

| 立上がりエッジでカウントします.(本実験ではこの設定を使用します) | 0 | 0 |

| 立下がりエッジでカウントします. | 0 | 1 |

| 立上がり/立下がりの両エッジでカウントします. | 1 | - |

| TPSC0〜2(タイマプロスケーラ):カウントするクロックを内部/外部クロックの選択,内部クロック周波数のプリスケーリングの是非などを設定します. |

| 説明 | TPSC2 | TPSC1 | TPSC0 |

| 内部クロック:φ(25MHz,0.04μsごと)でカウントします. | 0 | 0 | 0 |

| 内部クロック:φ/2(12.5MHz,0.08μsごと)でカウントします. | 0 | 0 | 1 |

| 内部クロック:φ/4(6.25MHz,0.16μsごと)でカウントします. | 0 | 1 | 0 |

| 内部クロック:φ/8(3.125MHz,0.32μsごと)でカウントします.(本実験ではこの設定を使用します) | 0 | 1 | 1 |

| 外部クロックA:TCLKA入力でカウントします. | 1 | 0 | 0 |

| 外部クロックB:TCLKB入力でカウントします. | 1 | 0 | 1 |

| 外部クロックC:TCLKC入力でカウントします. | 1 | 1 | 0 |

| 外部クロックD:TCLKD入力でカウントします. | 1 | 1 | 1 |

|

ただしφ:CPUのクロック周波数(本実験では25MHz)です.本実験では外部クロックは使用しません. |

|

用語: |

|

|

|